【学术科研】中国科学院计算技术研究所处理器芯片全国重点实验室两篇论文获MICRO2023录用

在2023年的国际计算机体系结构旗舰会议MICRO(IEEE/ACM International Symposium on Microarchitecture,CCF A类)上,中国科学院计算技术研究所处理器芯片全国重点实验室(以下简称全重实验室)两篇论文《Cambricon-R: A Fully Fused Accelerator for Real-Time Learning of Neural Scene Representation》和《Cambricon-U: A Systolic Random Increment Memory Architecture for Unary Computing》获录用。

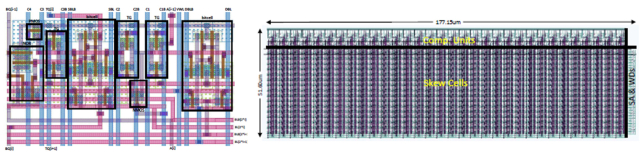

神经渲染场处理过程和Cambricon-R结构

Cambricon-R是一种全融合的神经场景表示算法加速器体系结构。神经场景表示算法是一种新型三维场景编码算法,具有高准确度和低成本的优势。然而,该算法的处理流程复杂,并引入了海量不规整的细粒度访存。在现有处理器(如GPU和NPU)上处理神经场景表示算法时,由于缺少专用的硬件流水线以及片上访存存在严重的板块冲突问题,使得硬件利用率极低,算法性能很差。这极大地限制了神经场景表示算法在AR/VR等实时交互式场景中的应用。

此次提出的Cambricon-R加速器通过设计逐光线的硬件流水线和专用的片上访存系统,避免了绝大多数的片外访存并解决了片上访存的板块冲突问题,极大地提升了运算单元的利用率。Cambricon-R与英伟达的A100 GPU相比,在12个典型3D场景数据集上实现了至少两个数量级的性能和能效提升,使得神经场景表示算法的运算可以达到交互式应用的性能要求。

Skew单元和RIM结构

Cambricon-U 是一种面向一元计算的低功耗深度学习处理器体系结构。一元计算由于只需要单个逻辑门对串行比特流进行算术运算,因此能够在低功耗设备上高效处理神经网络。然而,一元计算仍然面临着能效瓶颈,因为存储串行的一元比特流需要将比特流累加成大位宽的二进制数。由于累加过程中的进位传递,此大位宽二进制数需要在每个时钟周期激活所有比特,使累加占据总功耗的32%~70%。

此次提出的 Cambricon-U 架构通过偏斜数据格式(skew number)实现了低功耗的累加。Cambricon-U每次累加只需要激活每个数字中的最多3个比特(而非所有比特)。Cambricon-U 与最新的一元计算架构 uSystolic 相比,降低了51% 的累加功耗,实现了 1.18-1.45 倍的能效比,而只引入了-1.9%~+0.77% 的面积开销。

MICRO、ISCA、ASPLOS和HPCA等四个CCF A类会议并称计算机体系结构领域的四大国际学术会议。MICRO是四大会议中历史最悠久的。自1968年创办以来,截止2022年55届MICRO会议总共收录论文2047篇,中国大陆高校、科研机构和企业一共发表了52篇论文。此次全重实验室获得录用的两篇论文均来自智能处理器团队。目前,全重实验室智能处理器团队在MICRO上共发表6篇,曾获MICRO最佳论文奖(2014)和最佳论文提名奖(2022)。智能处理器团队在体系结构方面深耕多年,提出了国际上首个深度学习处理器架构(与法国Inria合作),研制了国际上首个深度学习处理器原型芯片,获得了处理器芯片领域首个国家自然科学奖。